US009941007B2

# (12) United States Patent Peddle et al.

## (54) SOLID STATE DRIVE ARCHITECTURES

(71) Applicant: THSTYME BERMUDA LIMITED,

Hamilton (BM)

(72) Inventors: Charles I. Peddle, Santa Cruz, CA

(US); Martin Snelgrove, Toronto (CA); Robert Neil McKenzie, Toronto (CA); Xavier Snelgrove, Toronto (CA)

(73) Assignee: Thstyme Bermuda Limited (BM)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 14/517,318

(22) Filed: Oct. 17, 2014

(65) Prior Publication Data

US 2015/0046625 A1 Feb. 12, 2015

### Related U.S. Application Data

- (63) Continuation of application No. PCT/US2013/070789, filed on Nov. 19, 2013.

- (60) Provisional application No. 61/728,394, filed on Nov. 20, 2012, provisional application No. 61/775,327, filed on Mar. 8, 2013.

| (51) | Int. Cl.     |           |

|------|--------------|-----------|

|      | G06F 9/45    | (2006.01) |

|      | G06F 12/08   | (2016.01) |

|      | G06F 12/0808 | (2016.01) |

|      | G06F 12/0815 | (2016.01) |

|      | G11C 14/00   | (2006.01) |

|      | G06F 12/02   | (2006.01) |

|      | G06F 13/28   | (2006.01) |

|      | G11C 11/4063 | (2006.01) |

|      | G11C 16/10   | (2006.01) |

|      | G06F 3/06    | (2006.01) |

|      | G11C 16/04   | (2006.01) |

|      |              |           |

### (10) Patent No.: US 9,941,007 B2

(45) **Date of Patent:** Apr. 10, 2018

#### (52) U.S. Cl.

CPC ...... *G11C 14/0018* (2013.01); *G06F 12/0246* (2013.01); *G06F 13/28* (2013.01); *G11C 11/4063* (2013.01); *G11C 16/10* (2013.01); *G06F 3/0688* (2013.01); *G06F 2212/7201* (2013.01); *G11C 16/0408* (2013.01)

58) Field of Classification Search

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 6,782,410 | B1*  | 8/2004 | Bhagat   | G06F 9/5027 |

|-----------|------|--------|----------|-------------|

|           |      |        |          | 709/201     |

| 6,842,377 | B2 * | 1/2005 | Takano   |             |

|           |      |        |          | 365/185.21  |

| 7,017,011 | B2 * | 3/2006 | Lesmanne |             |

|           |      |        |          | 711/141     |

| 7,196,942 | B2 * | 3/2007 | Khurana  |             |

|           |      |        | _        | 326/38      |

| 7,269,715 | B2 * | 9/2007 | Le       |             |

|           |      |        |          | 712/215     |

|           |      |        |          |             |

(Continued)

Primary Examiner — Tuan Thai

Assistant Examiner — Mohamed Gebril

(74) Attorney, Agent, or Firm — Fabian Vancott; Steven

L. Nichols

### (57) ABSTRACT

A solid state drive includes DRAM logical flash and flash memory, in which system processor reads and writes only to the DRAM logical flash which minimizes writes to the flash memory. A method for operation of a solid state flash device includes writing, by a CPU, to a solid state drive by sending commands and data to DRAM logical flash using flash commands and formatting.

### 30 Claims, 15 Drawing Sheets

## US 9,941,007 B2

Page 2

| (56)                         |      | Referen | nces Cited                          | 2010/0042773                 | A1*   | 2/2010  | Yeh G06F 12/0804                    |

|------------------------------|------|---------|-------------------------------------|------------------------------|-------|---------|-------------------------------------|

|                              | U.S. | PATENT  | DOCUMENTS                           | 2010/0046267                 | A1*   | 2/2010  | 711/103<br>Yan G11C 16/24<br>365/51 |

| 7,321,955                    | B2 * | 1/2008  | Ohmura                              | 2010/0050016                 | A1*   | 2/2010  | Franklin G06F 11/0727<br>714/6.32   |

| 7,512,736                    | B1 * | 3/2009  | Overby G06F 3/0607<br>707/999,202   | 2010/0125712                 | A1*   | 5/2010  | Murase G06F 11/1458 711/162         |

| 7,535,787                    | B2 * | 5/2009  | Elmhurst G11C 16/3418<br>365/185.09 | 2010/0138591                 | A1*   | 6/2010  | Yano G11C 29/702<br>711/103         |

| 7,580,277                    | B2 * | 8/2009  | Fuji G11C 11/406<br>365/148         | 2010/0202238<br>2010/0241785 |       |         | Moshayedi et al.<br>Chen            |

| 7,711,890                    | B2 * |         | Lasser G06F 12/0246<br>711/103      | 2010/0241789                 | A1*   | 9/2010  | 711/6<br>Chu G06F 12/0246           |

| 7,945,825                    |      |         | Cohen G06F 11/1072<br>714/721       | 2010/0293420                 | A1*   | 11/2010 | 711/103<br>Kapil G06F 12/08         |

| 8,230,193                    |      |         | Klemm G06F 3/0608<br>711/114        | 2010/0332780                 | A1*   | 12/2010 | 714/710<br>Furuya G06F 3/0689       |

| 8,566,546                    |      |         | Marshak G06F 3/0604 711/112         | 2011/0004722                 | A1*   | 1/2011  | 711/162<br>Jeddeloh G06F 12/00      |

| 8,595,449                    |      |         | Kund G11C 7/04<br>365/113           | 2011/0047324                 | A1*   | 2/2011  | 711/103<br>Norman G06F 12/0246      |

| 8,990,527<br>2004/0068621    |      |         | Linstead                            | 2011/0066837                 | A1*   | 3/2011  | 711/103<br>Lee G06F 9/4401          |

| 2004/008821                  |      |         | 711/144 Chefalas                    | 2011/0145485                 |       |         | 713/2<br>Chun                       |

| 2006/0080501                 |      |         | 711/113<br>Auerbach                 | 2011/0202735                 |       |         | Kono G06F 11/1451<br>711/162        |

| 2006/0202999                 |      |         | 711/112 Thornton G06F 12/145        |                              |       |         | McCune G06F 17/30221 714/54         |

| 2007/0008328                 |      |         | 345/531<br>MacWilliams G06F 12/0646 | 2012/0110293                 |       |         | Yang G06F 9/45558 711/170           |

| 2007/0133331                 |      |         | 345/530<br>Park G06F 11/106         | 2012/0198107                 |       |         | McKean G06F 13/18 710/40            |

| 2007/0255898                 | A1*  | 11/2007 | 365/222<br>Nishide G06F 12/0866     | 2012/0246392                 |       |         | Cheon G06F 12/0871 711/103          |

| 2008/0028136                 | A1*  | 1/2008  | 711/113<br>Schakel G06F 13/1636     | 2012/0284587                 |       |         | Yu G06F 3/0608<br>714/773           |

| 2008/0104314                 | A1*  | 5/2008  | 711/106<br>Rajan G06F 13/4243       | 2013/0007373                 |       |         | Beckmann G06F 12/126<br>711/136     |

| 2008/0250189                 |      |         | 711/105<br>Cheng et al 711/100      | 2013/0067161                 |       |         | Chandra G06F 13/12<br>711/114       |

| 2009/0094413                 |      |         | Lehr                                | 2013/0080805                 |       |         | Vick                                |

| 2009/0113119                 |      |         | Oribe                               | 2013/0111129                 |       |         | Maki                                |

| 2009/0161466                 |      |         | Hamilton G11C 16/10<br>365/222      | 2013/0152097                 |       |         | Boctor G06F 9/505<br>718/103        |

| 2009/0172257<br>2009/0228648 |      |         | Prins                               | 2013/0326270                 |       |         | Chen                                |

|                              |      |         | 711/114<br>Lim                      | 2014/0003114                 | A1*   | 1/2014  | Pellizzer H01L 27/2481<br>365/63    |

| 2007/0202101                 | 711  | 11/2009 | 709/203                             | * cited by exar              | niner |         |                                     |

Fig. 1

Fig. 3

Fig. 4

# WRITE OPERATION 500 CPU sends a write command and places data to be written to the SSD on the SATA bus 505 The write command is transferred to the master controller, which instructs the Logical Flash Controller to accept the data and transfer it the DRAM logical flash. As part of each write, the CPU sends multiple redundant writes to update the FAT table for any file being changed. <u>510</u> The logical flash controller sets up the SATA DMA and manages the transfer of the data into DRAM logical flash <u>515</u> The logical flash controller manages the data as flash files, including consolidating and update the data stored in the DRAM logical flash <u>520</u> The master controller determines if and when data should be transferred from the DRAM logical flash to the flash memory. <u>525</u>

Fig. 5B

When the master controller makes the decision to write the data from the DRAM logical flash to the flash memory devices, it sends a command to the logical flash controller that identifies the data that is to be transferred and alerts the bus controller of the data transfer

<u>530</u>

The master controller sends command data (read and write commands) onto the internal bus that alerts the flash controllers that data is coming/going. The logical flash controller sets the appropriate register values to configure the bus DMA for the transfer and the data identified by the master controller is placed on the high speed internal bus by the bus DMA

<u>535</u>

The master controller begins transfer of the data with specific data segments addressed to individual flash controllers

<u>540</u>

During a data transfer, the master controller sequentially directs data to a first flash interface during a first DMA cycle and then to a second flash interface during a second DMA cycle. Within the each flash memory device, the data is directed to flash registers to be sequentially written to flash chips in the device.

<u>545</u>

Simultaneously, the data is being read out of the registers in the flash controllers to the flash die in parallel at 40 MB per second

550

Fig. 5B (cont.)

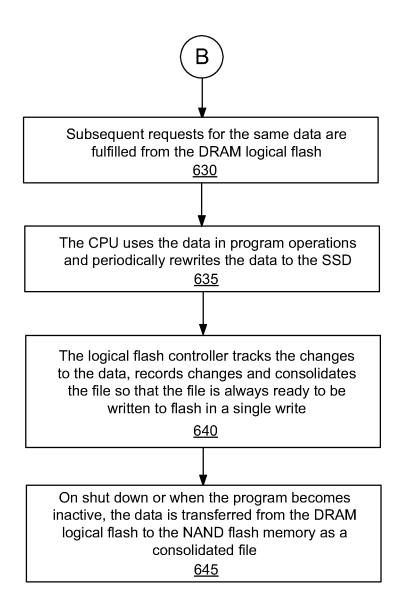

Fig. 6B

Fig. 6B (cont.)

SNAPSHOT OPERATION 700

# User/Operating system/CPU decides that a snapshot should be saved

705

The state of the computing device is saved to a protected area ("Snapshot Area")on the DRAM logical flash including all the data in the CPU memory. This transfer is not performed using logical records and the data is not stored using logical records or block look up tables. Tables stored with the data in the Snapshot area are used to index/ organize the various snapshots. Typically, the snapshots are organized by the time the snapshots were taken.

<u>710</u>

When the CPU sends an command or the power circuit sends an interrupt, a snapshot saving sequence stores the last two snapshots as a priority into the flash memory. This process also does not use logical records or block lookup tables. Designated blocks are ready to receive the snapshot data. Relevant data about the organization of the snapshots and how to retrieve them is stored in tables with the snapshots

<u>715</u>

When the system recovers/restarts the snap shot recovery code retrieves the snap shot from flash to the DRAM logical flash and back into the CPU memory

720

Fig. 7

Programs are stored in storage portion of a protected program area of SSD during manufacturing/configuration. The user is unable to directly access the protected program area.

<u>805</u>

When a user receives appropriate permission to use a particular program, the program is transferred from the storage portion to the active portion of the protected program area

<u>810</u>

To prepare to use one or more programs in the active area, the program files are moved into a protected program area of the DRAM logical flash. This transfer does not use logical records, but is a bulk transfer. The protected program area is not directly accessible to the user.

815

The programs in the protected program area of the DRAM logical flash are transferred to the CPU memory for execution. The program files are not typically included in snapshots or dump/restore operations because the program files are not changed during execution. Files generated by the program files, including configuration and data files can be included in snapshots and dump/recovery operations

<u>820</u>

Updates to the program files, including program files that the user does not yet have permission to access can be streamed from a network to the protected program area of the SSD using background operations

825

Fig. 8

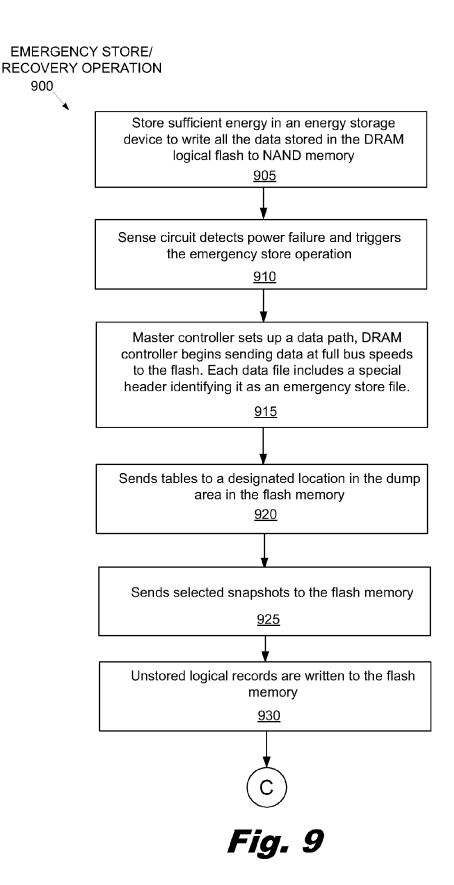

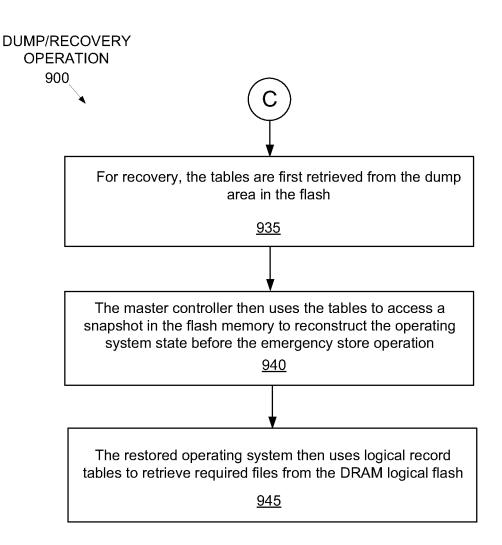

Fig. 9 (cont.)

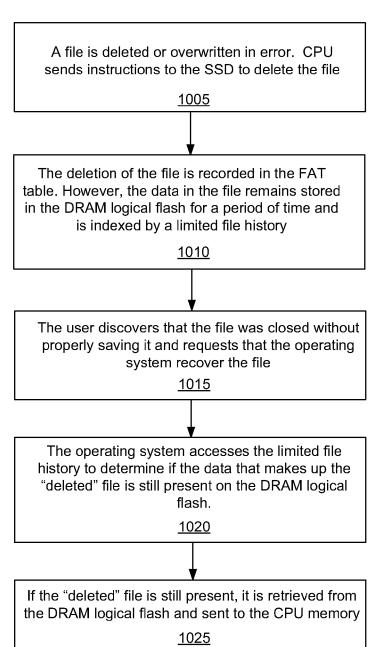

Fig. 10

### SOLID STATE DRIVE ARCHITECTURES

#### RELATED APPLICATIONS

The present application claims benefit and is a continuation of International Application No. PCT/US2013/070789, filed Nov. 19, 2013, which claims the benefit of U.S. Provisional Application No. 61/728,394, filed Nov. 20, 2014 and U.S. Provisional Application No. 61/775,327, filed Mar. 8, 2013. These applications are incorporated herein by reference in their entireties.

### FIELD OF THE INVENTION

This application is related to solid state drive architectures.

### BACKGROUND

Computing devices preserve program executables and data in nonvolatile memory. This makes the files available to the computing devices after being restarted or after power interruptions. Traditionally, the preferred nonvolatile storage for large files has been a hard disk drive. Hard disk drives 25 include rotating rigid platters on a motor driven spindle. Data is magnetically read from and written to the platter by heads that float on a film of air above the platters. These platters typically spin at speeds of between 4,200 and 15,000 revolutions per minute (rpm). Hard disk drives have a number of disadvantages, including access times that are related to the mechanical nature of the rotating disks and moving heads, high power consumption, mechanical failure, and low shock resistance.

Solid State Drives (SSDs) are nonvolatile storage devices that use integrated circuits to store data and consequently contain no moving parts. SSDs have a number of advantages over hard disk drives including higher shock resistance, lower access times, and more variable form factors. Additionally SSDs typically consume far less power during operation than hard disk drives. Consequently, SSDs allow for smaller, thinner device profiles and for longer operation on a battery charge.

### BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings illustrate various examples of the principles described herein and are a part of the specification. The illustrated examples are merely examples 50 and do not limit the scope of the claims.

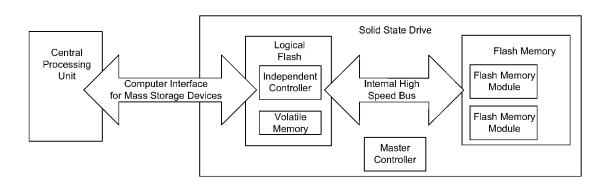

- FIG. 1 is a block diagram of an illustrative solid state drive architecture, according to one example of principles described herein.

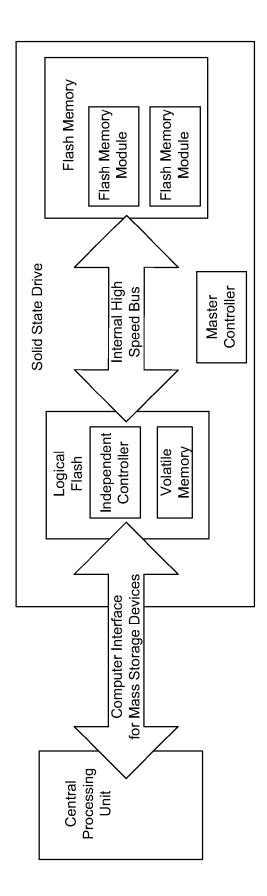

- FIG. 2 is a block diagram of a flash memory module, 55 according to one example of principles described herein.

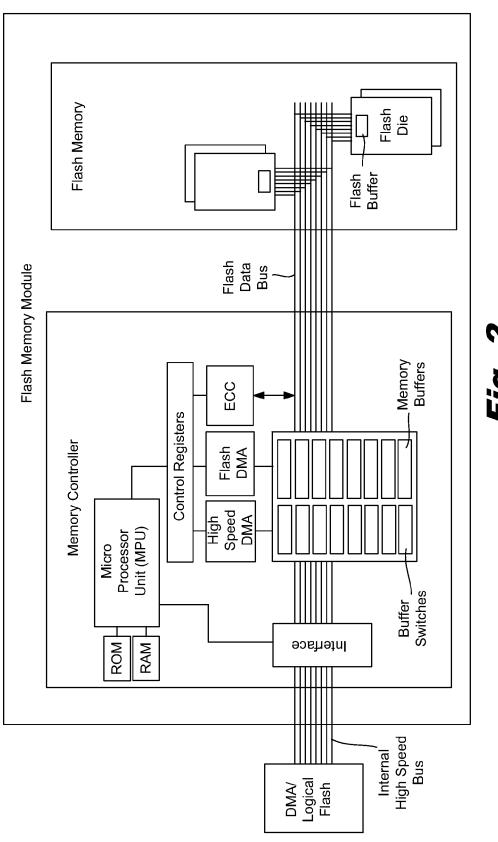

- FIG. 3 is a block diagram of an illustrative solid state drive architecture that incorporates flash memory modules shown in FIG. 2, according to one example of principles described herein.

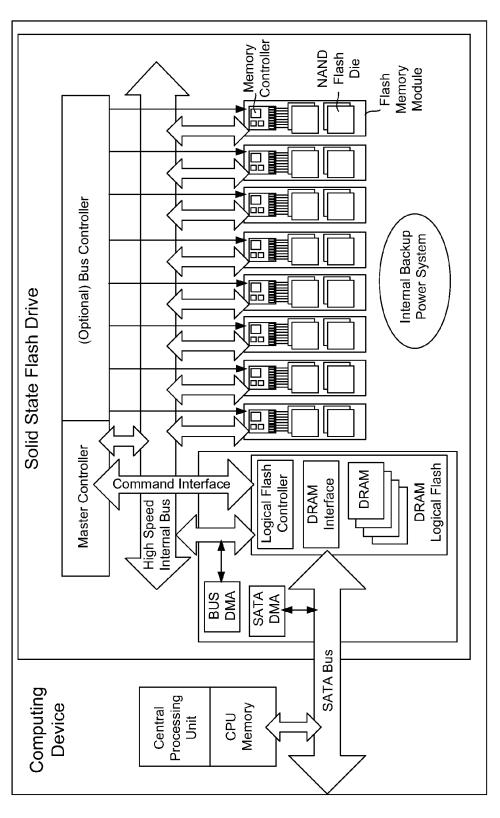

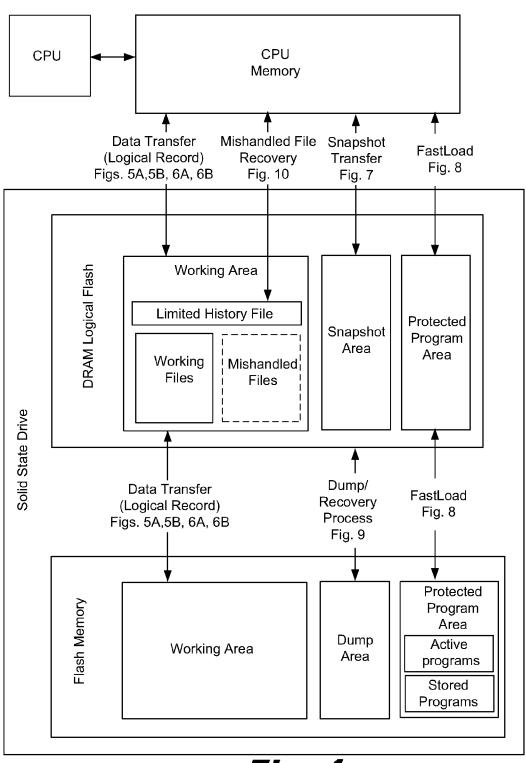

- FIG. **4** is a diagram various interactions and processes that occur between the CPU/CPU memory, DRAM logical flash, and flash memory, according to one example of principles described herein.

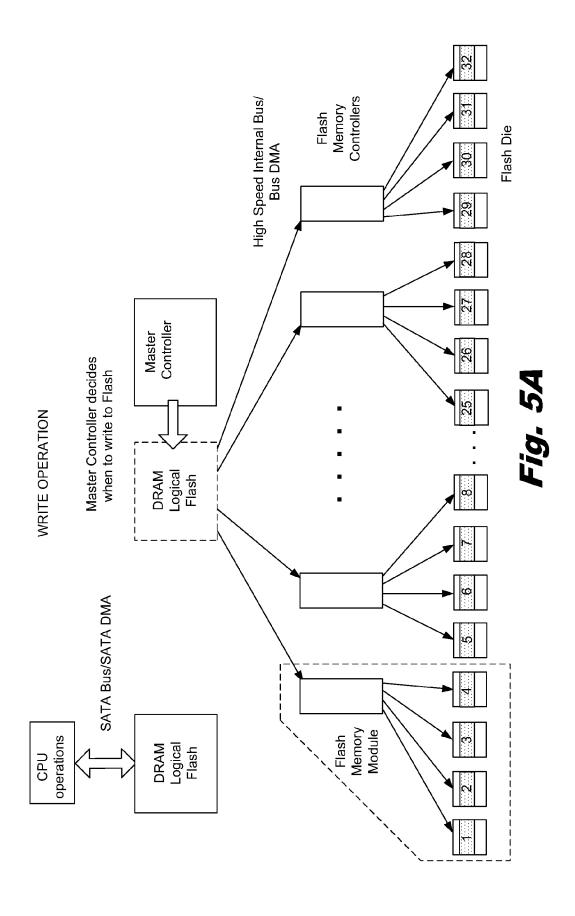

- FIG. 5A shows data flow during writing of data to the 65 solid state drive, according to one example of principles described herein.

2

FIG. **5**B is a flow chart describing a method for writing data to the solid state drive, according to one example of principles described herein.

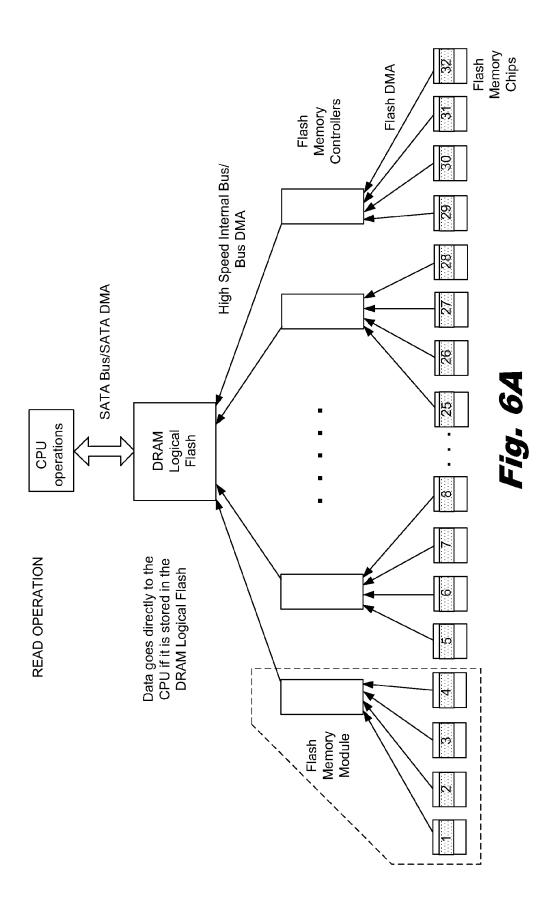

FIG. 6A shows data flow during reading data from the solid state drive to CPU memory, according to one example of principles described herein.

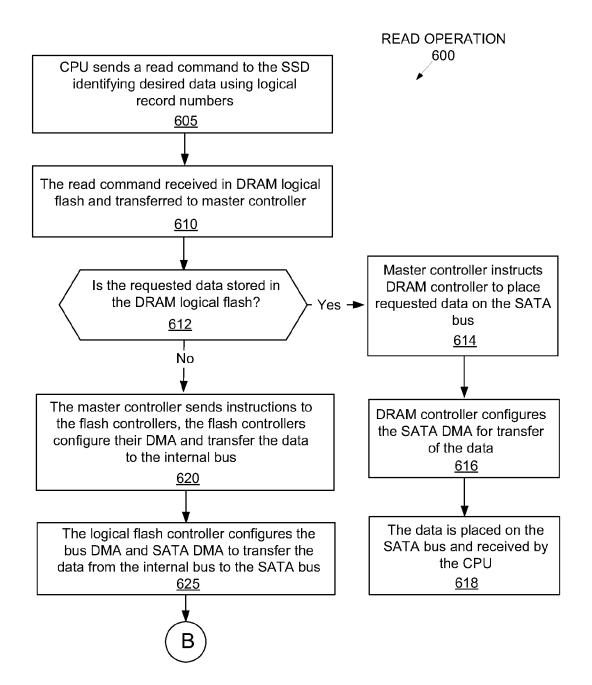

FIG. **6**B is a flow chart describing a method for reading data from the solid state drive to CPU memory, according to one example of principles described herein.

FIG. 7 is a flow chart showing a method for saving snapshot of a system state, according to one example of principles described herein.

FIG. **8** is a flow chart of an illustrative method for fast loading program files from the SSD to the CPU memory, according to one example of principles described herein.

FIG. 9 is a flow chart of a method for data dump/recovery, according to one example of principles described herein.

FIG. 10 is a flow chart of a method for mishandled file recovery, according to one example of principles described herein.

Throughout the drawings, identical reference numbers designate similar, but not necessarily identical, elements.

#### DETAILED DESCRIPTION

Solid State Drives (SSDs) are nonvolatile storage devices that use integrated circuits, such as NAND flash memory, to store data. SSDs have a number of advantages, such as high shock resistance, low power requirements, faster access times, and more variable form factors. However, integrated circuits that are used as memory in solid state drives have a limited lifetime. Typical specifications for NAND flash specify that NAND flash can only reliability be used for 1000-3000 write/erase cycles before failure. This lifetime limitation is particularly troublesome because, in the current architectures, a block of NAND flash must be erased and rewritten each time any part of the data contained with the block is changed. Thus, the more frequently a SSD drive is used, the faster it will fail. Many operating systems write to the non-volatile memory frequently. For example, File Access Tables (FAT tables) are rewritten every time a file changes. Each FAT table update includes multiple erase/ write cycles. An alternative file system is the New Technology File System (NTFS) which is a proprietary file system 45 developed by Microsoft® and is the default file system for the Windows® family of operating systems. NTFS has improved support for metadata, and the use of advanced data structures to improve performance, reliability, and disk space utilization, plus additional extensions, such as security access control lists (ACL) and file system journaling. NTFS writes to the SSD drive even more frequently that the FAT system. Additionally, many operating systems periodically save "snapshots" of the current state of the computing device into nonvolatile memory. While this can be beneficial in recovering the operation of the computing device, routinely saving the large snapshots on to the NAND flash can significantly shorten the lifetime of the SSD. Consequently, SSDs can fail to meet the customer expectations and may require frequent replacement.

A number of principles are described below that allow for flash memory to be used effectively as non-volatile storage despite its finite number of erase/write cycles. The solid state drive (SSD) architectures described below address the limitations of NAND flash memory by creating DRAM logical flash to act as an intermediary between the flash memory and then independently assessing when data should be written to the NAND flash memory. This significantly improves the

operational speed and lifetime of the SSD and allows the SDD to be used as a plug and play alternative to hard disk drives

Data usage within a computing device typically falls into two categories: a high amount of usage during creation/ 5 manipulation of the data and then a far lower amount of usage when the data is archived or stored as a functioning program. The illustrative SSD separates the process of storing data related to the transient state of the computing device and the permanent storage capability of the flash.

When the computing device is powered down, the data stored by the volatile memory of the computing device is lost. The SSD described below facilitates the creation of data files by allowing the data to be stored during development of the program or data file and protecting against data loss 15 when the computing device powers down.

The SSD includes several flash interface controllers managing an optimum number of flash memory devices. In a simple system like a USB2 device one intermediate controller can be used to manage the flash directly. However, in 20 a high speed system several controllers can be operated in parallel to manage the data much more rapidly. Principles described below can also be applied to a wide variety of bus and device technologies, including SATA 3 (500 megabytes per second), USB 3.0 "Superspeed" devices, including USB 25 3.0 solid state drives and storage devices. The USB 3.0 specification specifies transfer rates of up to 4.8 gigabits per second, increased maximum bus power and more efficient power management.

In the following description, for purposes of explanation, 30 numerous specific details are set forth in order to provide a thorough understanding of the present systems and methods. It will be apparent, however, to one skilled in the art that the present apparatus, systems and methods may be practiced without these specific details. Reference in the specification 35 to "an example" or similar language means that a particular feature, structure, or characteristic described in connection with the example is included in at least that one example, but not necessarily in other examples.

In several instances below, a controller is described that 40 includes at least one microprocessor, read only memory (ROM) and random access memory (RAM). The microprocessor, ROM and RAM work together to implement the functions of the controller. The use of a different microprocessor with different controls and/or hardware implementation can be used to implement the principles described herein.

FIG. 1 shows one implementation of a solid state drive that includes logical flash and nonvolatile flash memory. The logical flash includes an independent controller and a seg- 50 ment of volatile memory. The logical flash is configured to implement all the functions of a flash controller such that the central processing unit (CPU) thinks it is reading and writing to flash, when it is actually reading and writing to logical flash. The logical flash implements flash memory behavior, 55 but without the lifetime, speed, or addressing limitations of flash memory. The logical flash stores files in the same way as the flash memory and responds to flash commands. Further, the logical flash uses the FAT or NTFS table, updates logical records, combines files, and is attached to a 60 SATA 3 bus. Because the volatile memory of the logical flash has a virtually unlimited number of read/write cycles, the system processor and operating system can store as many updates and snap shots as desired. Further, the logical flash is extremely fast in both reading and writing data. The 65 CPU reads from and writes exclusively to the logical flash while writes and reads to the flash memory are controlled

4

exclusively by the solid state drive. The use of logical flash allows all flash commands to be handled at full interface speeds and minimizes writes to the flash memory. This is different from caching, because caching ultimately writes everything to flash memory and is implemented only to increase speed and to handle short read and writes.

A master controller within the SSD independently determines when data should be transferred to or from the flash memory. This significantly reduces the number of write/erase cycles for the flash memory because the CPU does not directly access the flash memory.

The flash memory includes a number of flash memory modules. Each flash memory module includes an independent controller and a number of flash die. By using independent controllers, the SSD can perform multiple operations in parallel. This leads to significantly faster read and write times.

The paragraphs below describe a variety of principles for developing an SSD that incorporates logical flash and multiple controllers. SSDs are currently more expensive per gigabyte of storage than hard disk drives. This is primarily due to the cost of the nonvolatile memory die that are used to store the data in the SSD. The memory die are typically flash memory, although other types of memory have been proposed, including Ferroelectric Random Access Memory (FeRAM), Magnetoresistive Random Access Memory (MRAM), Programmable Metallization Cell (PMC), Phase-Change Memory (PCM), and other technologies. Each of these types of nonvolatile memory types has advantages and disadvantages. However, flash memory is the most mature technology and has the lowest cost per unit of storage capacity. There are two predominant types of flash memory: NOR type and NAND type. Both NOR and NAND flash store data in memory cells made from floating gate transistors. These floating gate transistors have a finite number of program-erase cycles before wear begins to deteriorate the integrity of the storage. For example, NOR flash memory may have a typical endurance rating of 100,000 cycles and NAND flash memory may have a typical endurance ratings between 1,000 to 3000 cycles.

NOR type flash memory allows for a single byte to be written and/or read independently. However, this random access feature makes NOR memory less dense per unit area and more expensive per unit of storage. NAND type flash is very high density and has a correspondingly lower cost per unit of storage. However, in current chip architectures, NAND type flash must be read and programmed in larger segments called blocks. This limitation is significant because altering a single bit in a block requires the erasure and rewriting of the entire written space in a block. For purposes of explanation, NAND type flash will be used in illustrative examples of solid state drive architectures. However, the principles described herein can be applied to a wide variety of nonvolatile memory types.

As discussed above, NAND type flash is inexpensive and compact but has the disadvantages of having a finite number of program-erase cycles before wear begins to deteriorate the integrity of the storage. This challenge is compounded by fact that, while NAND type flash can be read at the bit level, NAND type flash must be written and erased in large segments ("blocks") rather than at the bit level. Consequently, when any bit in a block changes, the all the data in the block must be copied to a new block. During the copying process, the new bit(s) are incorporated into the data stored on the new block. The old block is then erased and used again. Programs and operating systems on many computing devices frequently read and write to the hard drive, which

could lead to rapid degradation of the NAND flash. In these industry standard operations, changing even one bit in a block requires the copying and erasure of the entire block. In the discussion below, principles are described that provide from holding a block until it is full and only updating the 5 pages that have already been written.

5

In some Apple® operating systems, the user's files are continuously written to the hard drive to allow the user to restore the machine to a previous state. Not only does the system recover to latest state, there is a program called a 10 "time machine" that allows the system to be restored to any previous state for months before. This program compresses the snapshots and allows recovery to a day but not any period during that day. However, the snapshots can be maintained so that recovery to a particular point for the 15 previous few days is possible. This time machine feature can be very useful in recovering files that were mishandled or lost. Recovering to time before the mistake was made allows for fully recovery of the file and system state.

These and other frequent write operations can lead to the 20 early failure of flash memory because the limited amount of write/erase cycles can quickly be exceeded. Every new write requires a copy of the old data to a new block to add the new data. As discussed above, each memory location in the NAND memory can only be updated on the order of 1,000 25 to 3,000 times without substantially increasing the likelihood of failure. There are many algorithms that try to work around this problem, such as over-provisioning the memory with spares and wear leveling algorithms that attempt to spread the wear uniformly over the entire flash memory 30 rather than concentrating it in the same blocks. However, these techniques may increase the cost and decrease the performance of solid state drives.

The examples below describe various solid state drive (SSD) architectures, methods and principles. These SSDs 35 incorporate flash memory for nonvolatile storage and are designed to have an order of magnitude longer lifetime than conventional SSDs and operate at full bus speeds despite the limitations of the flash memory.

Illustrative Flash Memory Module

FIG. 2 is a diagram of an illustrative flash memory module. As discussed above, flash memory is nonvolatile computer storage that can be electrically erased and reprogrammed. As discussed above, flash memory has a high resistance to mechanical shock, small foot print, relatively 45 fast read times that are comparable to dynamic Random Access Memory (RAM), is energy efficient and can store data for years without power. Flash memory is used in a variety of applications, including personal computers, mobile devices, digital cameras, video games, scientific 50 instrumentation, industrial robots, medical electronics and other devices. Flash memory has several limitations, including slow write times and limited lifetime. For flash memory, the write times are typically order of magnitude greater than the read times. The lifetime of various types of flash memory 55 typically ranges from 1000 to 3000 erase cycles. The erasure of the flash memory causes incremental damage that eventually leads to failure of the memory mechanism in the flash memory.

The illustrative flash memory module shown in FIG. 2 60 includes a number of NAND flash die. The memory controller includes a processor, a small amount of Random Access Memory (RAM), a small amount of Read Only Memory (ROM), and a number of memory buffers. Examples of this memory controller are given U.S. Pat. App. 65 No. 61/774,175; entitled "High Speed USB Controllers," to Charles I. Peddle, which is hereby incorporated by reference

above in its entirety. For example, the memory controller may be based on a 6502 processor, with 20 kilobytes of processor addressable RAM, 40 kilobytes of ROM to store operating code, and eight memory buffers. The memory controller accepts data from an external bus, accumulates the data in the buffers, and writes the data to the NAND flash die. The external bus may be a USB bus or a high-speed internal bus.

The memory controller also includes a high speed Direct Memory Access (DMA) and a flash DMA. In general, a DMA protocol includes an address counter that automatically and progressively increments the memory addresses during data transfers. The DMA protocol also includes a counter that keeps track of the number of bytes transferred. To begin a DMA transfer, two commands are given, the memory location to start at and a count that tells the DMA how many bytes to transfer. The DMA independently transfers the data starting at the designated memory location until the count is exhausted. The purpose of the DMA protocol is to allow full speed transfers to and from a memory without the need for external inputs other than the memory clock and enables. This entirely eliminates the requirement for the microprocessor to directly be involved with data transfers. This enables higher transfer speeds because the data transfer is not limited by the microprocessor speed or interrupted when the MPU is redirected to a different task.

In this application there are two independent DMAs with different functionality. The high speed DMA ("bus DMA") controls the transfer of data from the high speed bus to a bank of memory buffers and the flash DMA transfers data to and from the flash. In one embodiment, data transfer from the high-speed bus to the memory buffers is the highest priority process and is interrupt driven. Data movement to or from the flash is done with polling because the process can be interrupted with little disturbance. Further, the polling generates positive control on the timing signals to the flash memory.

The use of two separate DMA modules (the high speed DMA module and the flash DMA module) provides several advantages. First, by including two separate DMA modules, data can be simultaneously written to and read from the memory buffers. Additionally, the separate DMA modules can operate differently and be controlled differently to facilitate data transfers. For example, the high speed DMA may be operating on a high speed clock and write data to one memory buffer while the flash DMA is reading data out of a different memory buffer at slower speeds. In contrast, the flash DMA may operate on a flash clock and be operated by polling. Additionally, the flash memory module generates, stores, and uses error correction code (ECC) to automatically recover data that has a limited number of errors due to write and/or storage failure. In addition to the data received on the high speed bus, the flash memory module also writes additional information to the flash memory including wear number, logical record number, update number, and other data. This process is described in greater detail below. The registers can run at various clock rates and be switched between various functions.

The structure and architecture given above is only one example of a flash memory device. A variety of other structures could be used. For example, larger memory buffers, larger sector sizes, more memory buffers, different numbers of memory buffers and different numbers flash die could be included in the architecture.

Illustrative Solid State Drive Architecture

FIG. 3 shows an illustrative example of a SSD architecture that incorporates a number of flash memory modules

such as those described above with respect to FIG. 2. The SSD architecture is capable of sustaining SATA data rates and mitigating the limited lifetime of the NAND flash memory. In this example, a central processing unit (CPU) external to the SSD is connected to a SATA bus. The SSD drive accepts data input, commands, and outputs data via the SATA bus. This output data is initially stored in DRAM logical flash. The DRAM logical flash includes a DRAM controller and a large bank of Dynamic Random Access Memory (DRAM). The DRAM logical flash is connected to a high speed internal bus. In addition to the connection to the DRAM logical flash, the high speed internal bus is connected to a bank of flash memory devices, and a master controller. In some embodiments, there may be a separate bus controller that controls operation of the high speed 15 internal bus. Alternatively, the functionality of the master controller and bus controller can be combined so that the master controller performs the functions of the bus controller. The high speed internal bus allows bidirectional communication between any of these entities. The bus controller 20 (or master controller acting as a bus controller) independently selects the device that is going to receive or transmit data. This allows the data flow to be controlled for each device individually (and in some examples sequentially). For example, the DRAM controller can accept data from the 25 SATA bus while the bus controller is transferring data out of the DRAM and into the flash memory devices. These simultaneous operations allow for more efficient operation and higher overall throughput. Flash operations can have temporal variations so the final synchronization of the data 30 is done by the master/bus controller managing the high speed bus and coordinating with the logical flash controller. This balancing approach allows SATA interface or other interface to run at full bus speed when reading or writing to the SSD.

### Controllers

The SSD architecture uses a number of controllers to manage internal data flow. The master controller receives instructions from the central processing unit of the computing device and manages the operation of the solid state flash 40 drive to perform the instructions. The master controller directs the operation of the bus, flash memory controllers in each of the flash memory devices, and logical flash controller. In one implementation, each of these controllers is a simple microprocessor system as described. According to 45 one illustrative example, each of the controllers (master controller and optional Bus controller, DRAM controller, eight flash controllers) is a completely independent system with its own microprocessor, ROM for storing code, RAM, and bank of registers. For example, the controllers may be 50 based a 6502 processor combined with 32 kilobytes of RAM and 24 kilobytes of ROM. The logical flash controller manages data transfer into and out of the DRAM by controlling DMA transfers and interfacing with the logical flash controller. The logical flash controller manages the DRAM 55 logical flash under the direction of the master controller. The master controller manages the transfer of data between the DRAM and flash memory. The individual flash controllers deal with the page mode structure for the flash memory, error correction, and wear leveling. The memory controller 60 in each of the flash memory devices manages transfer of data between the high speed internal bus and the NAND flash die.

The use of multiple internal controllers provides a number of benefits. The controllers can perform dedicated functions that are specifically adapted to the device they are controlling while flexibly coordinating with other controllers. For example, the memory controllers may interface with the 8

high speed bus at a first clock speed and then manage data being written to the NAND flash die at a different clock speed. Additionally, the memory controllers may signal the master controller when they have completed a task. This allows the master controller to intelligently allocate resources to maximize data transfer rates.

### Direct Memory Access Interfaces

Direct Memory Access (DMA) interfaces manage the transfer of data for each controller that is connected to a bus. As discussed above, DMA is a hardware implemented protocol that allows hardware subsystems within the computer to access system memory independently of a controller. The controller can initiate a transfer, do other work while the transfer is in progress, and receive a feedback from a DMA controller once the transfer is complete. For example, a SATA DMA handles transfer of data from the SATA bus to the DRAM Logical Flash. A bus DMA handles transfer of data between the DRAM Logical Flash and the high speed internal bus. Similarly, DMA interfaces between the high speed internal bus and each of the flash memory devices manage data transfer into and out of the flash memory devices.

Using DMA techniques maintains the speed for both writing the flash and transferring data to/from the interface.

25 As discussed above, a DMA protocol includes an address counter that automatically and progressively increments the memory addresses during data transfers. The purpose of the DMA protocol is to allow full speed transfers across an interface without external inputs other than the memory clock and enables. This entirely eliminates the requirement for a microprocessor to be directly involved with data transfers and enables higher transfer speeds because the data transfer is not limited by the controlling processor or interrupted when the controlling processor is redirected to a different task.

To begin a DMA transfer, the controlling processor may load control registers with addresses, a count for the number of DMA operations and other enabling functions. The data transfer then occurs as a function of the parameters in the control registers. The DMA may be configured such that other data may be added during the transfer such as error correction data, logical records, and housekeeping functions. The DMA protocol can trigger a variety of responses to signal the controlling processor that a data transfer is complete or to provide a status update. This allows the data to be accessed as soon as the DMA transfer is complete. Additionally, the use of interrupts to signal the status of data transfers allows for polling style parallel distribution of data between multiple memory storage components within the SSD.

### DRAM Logical Flash

The DRAM in the DRAM logical flash uses arrays of capacitors to store data. The capacitor may be either charged or discharged. These two states represent the two values of a bit. Since the capacitors leak charge, the state of the capacitor eventually fades unless the capacitor charge is refreshed periodically. This refreshing occurs over intervals on the order of 10 to 100 milliseconds. DRAM is very simple, has negligible read/write cycle wear, and can be very densely packed onto a die. Additionally, DRAM provides extremely fast write and read times (on the order of 10 to 100 nanoseconds). The operation of the DRAM is controlled by a DRAM controller. In this example, the DRAM has a total capacity of 8 Gigabytes of Double Data Rate type three Synchronous Dynamic Random Access Memory (DDR3 SDRAM). In other implementations, the DRAM may have larger (e.g. 16 GB Gigabytes) or smaller amount of memory.

For power management, the DRAM can operate at a clock speed of 800 Megahertz. However, any suitable clock speed and amount of DRAM can be included in the design. The DRAM logical flash stores files in the same way as flash and responds to flash commands. Further, the DRAM logical 5 flash uses a file allocation table, updates logical records, combines files, and is attached to a SATA bus.

DRAM logical flash is not cache for a number of reasons. For example, cache is an alternative location for the CPU to look for data. If the data isn't in the cache, the CPU accesses 10 the underlying nonvolatile memory. In contrast, the DRAM logical flash is the only memory in the SSD that is directly accessible to CPU. The actual NAND flash is under control of a master controller and is not directly accessible to the CPU. The DRAM logical flash acts as a gatekeeper between 15 the CPU and the NAND flash. By separating the NAND flash from the CPU instructions, the NAND flash is not subject to numerous peculiarities of the operating system, including frequent writes. This allows the operating system to run without modification while protecting the lifetime of 20 the NAND flash.

Data and files are only stored to the DRAM logical flash until deleted or no activity is observed. In general, data in the DRAM logical flash is organized by logical record for the user control of the data and referenced by the FAT table to 25 control the operations of the various data records. However, in some instances, the DRAM logical flash may receive, store, and transfer data without the use of logical records. For example, the Snapshot and FastLoad procedures described below do not use logical records. However, all the 30 data transfer modes the movement of data out of the DRAM logical flash to the flash memory is governed only by the master controller. The master controller may make decisions about when the data or files are moved out of the DRAM logical flash based on a number of factors, including the lack 35 of use of the file. CPU commands received by the master controller may have some influence on the master controller moving data into/out of the flash, but it is the master controller that makes actually makes the decision about retrieving data from or writing data. For example, if the CPU 40 requests a data file the master controller determines if the file is in the DRAM logical flash. If the requested data isn't in the DRAM logical flash, the master controller retrieves it from the flash and stores it in the DRAM logical flash.

In some instances, files and/or data may only be stored on 45 the DRAM logical flash and never transferred to the flash memory. For example, a temporary data file may be created for a transient operation (such as a search). In other examples, a file may be created for a letter or email that will be sent to another system or stored by a remote system. 50 When the file is sent to the remote system, the file can be deleted.

Cache appears to the CPU to have exactly the amount of physical memory that is actually present in the cache. In contrast, the DRAM logical flash appears to have a capacity 55 that is much greater than the physical capacity of the memory that makes up the DRAM logical flash. The DRAM logical flash appears to have a capacity that is equivalent to the total working nonvolatile memory of the NAND flash.

Cache appears to the CPU to be volatile memory. In 60 contrast, DRAM logical flash appears to be extremely fast nonvolatile memory. When a CPU writes data to cache, the CPU doesn't assume that the data is actually in nonvolatile storage. The CPU continues to manage the data flow until the data is actually stored in the nonvolatile storage that 65 follows the cache. When power is unexpectedly lost to the cache, the data in the cache is lost and the CPU must recover

10

without it. All cache transactions either fail or are written to nonvolatile flash memory increasing the wear and delaying

In contrast, the CPU and operating system assume that the DRAM logical flash is the nonvolatile memory storage. The DRAM logical flash reports that data written to it is stored on the nonvolatile flash memory even through it actually stored in the DRAM logical flash. When the power to the SSD is lost, the CPU correctly assumes the data stored in the DRAM logical flash is stored in nonvolatile memory. This is correct because the SSD has a self-contained and selfpowered system for dumping the data in the DRAM logical flash to NAND flash. In one implementation, the NAND flash is configured with an extra provision of spares to accommodate a data dump of all the data that can be stored in the DRAM logical flash.

Cache is designed to minimize access time to data stored in a slower memory. In typical cache operations, the cache writes data as quickly as possible to the nonvolatile storage but continues to hold the data written to minimize access times. In contrast, the DRAM logical flash is designed to minimize writes to the underlying memory. The master controller in the SSD only targets data that is not being used for transfer from the DRAM logical flash to the flash memory.

High Speed Internal Bus

As discussed above, the high speed internal bus allows bidirectional communication between any of these components connected with it. In one example, the master controller individually directs data to the memory controllers over the high speed internal bus. To implement the write transfer to the flash, the logical flash controller/interface connects the DRAM logical flash to the high speed internal bus and uses DRAM DMA to make the transfer to a designated file location. Using this technique, data could be directly transferred from the CPU, through the DRAM logical flash, to the flash memory. For example, high speed internal bus may be 8 bits wide and capable of operating at speeds of at least 400 megabytes (MB) per second. Data transfer rates over an 8 bit bus operating at 400 megahertz (or higher) would be approximately 400 megabytes per sec.

Flash Memory Devices

As discussed above with respect to FIG. 2, each of the flash memory devices includes a memory controller and a number of NAND flash die that make up the flash memory. The flash memory is divided into sectors, pages, blocks and planes. In this example, a sector is approximately 512 bytes with additional room for header and error correction code (ECC) information. In other implementations, the sector may be larger. A page is a group of sectors, a block is group of pages, and a plane is a collection of pages. In one example, a page includes 8192 bytes for data and additional room for header information. A block may be a group of 256 pages and a plane is a group of 2096 blocks. A device may include any number of planes. For example, a 32 gigabyte device may include 2 planes or 8,192 blocks. A 256 gigabyte device may include 16 planes or 65,536 blocks. Typically when a non-recoverable or repairable flash data error occurs in a sector, the entire block is marked as bad. However, using a page mode controller, only the offending page is marked as bad and is mapped around. This is further described in U.S. Pat. No. 8,122,319 to Charles I. Peddle, which is hereby incorporated by reference in its entirety.

As discussed above, an entire block of flash memory is traditionally considered unusable when a single bit in one of the pages in the block is inoperable. Consequently, a defective bit may reduce the storage capacity of the flash memory

by 128 KB or more. When multiple defective bits are dispersed among many blocks, a flash memory may fail to meet capacity standards and may be discarded. However, many completely functional pages remain within each failed block. As shown below, by identifying inoperable pages 5 rather than inoperable blocks, much of the storage capacity of the flash memory may be reclaimed.

Various commands are used to access a flash memory. For example, read and write commands to a flash memory may operate on a single page. Erase commands, however, affect 10 an entire block. With the exception of block erase operations, nearly all operations may be performed on a single page. Once the pages in a block are erased, they may be selectively written in a manner that avoids inoperable pages.

Although the flash memory itself may not include logic to 15 select only operable pages within a block, a memory controller may be configured to identify, select, and operate on only the operable pages. The memory controller may be implemented as a semiconductor chip separate and distinct from the flash memory. The memory controller coordinates 20 the transfer of data to and from the flash memory. The memory controller processes requests from external devices by sending appropriate commands and memory addresses to one or more flash devices. According to one embodiment, the memory controller may generate chip select, block 25 select, row select, and column select signals to transmit to one or more flash memories. The memory controller may also monitor control signals, status signals, timing constraints, and other aspects of data transfers to and from a flash memory device.

The memory controller may translate a virtual memory address (such as a logical record) from an external system to a physical address on one or more flash memory devices. A memory controller may receive a query from a processor requesting certain data. In response, the memory controller 35 may determine the corresponding block, page, and byte where the requested data is physically stored in one or more flash memory devices. The memory controller may then issue the correct sequence of control signals and memory address values to the flash memory device to retrieve the 40 requested data.

Similarly, the memory controller may translate write requests into an appropriate sequence of block erase, address select, and write commands to store data on a flash memory device. In effect, the memory controller may allow various 45 systems and components access to the storage of the flash memory devices while concealing the complexity of the page mode interface with the flash memory devices. For example, when previously written data in a flash memory device is updated, the old data as well as the new data is 50 written to a new block and the old block is erased. The memory controller may generate and execute the correct sequence of operations to carry out the storage operation. The memory controller may also identify which blocks contain a sufficient number of operable pages to complete an 55 operation. Where data is transferred from a source block to a destination block, the destination block is selected to contain at least the same amount of storage capacity as the source block, but the destination block may still include one or more inoperable pages or sectors.

To track the number of operable pages in within each block, the memory controller may build a "good page" table, a "bad block" table, a table that has a "good" or "bad" designation for each page of the memory, or other indicator. The "bad block" table may identify inoperable pages and 65 thus identify operable pages indirectly. The memory controller or other element may then be configured to read and

write to any page except those listed as inoperable. An indication of operable pages may include one or more references, pointers, addresses, tables, lists, sets, identifiers, labels, signs, tokens, codes, or equations, or other information that may allow an operable page to be identified.

12

In one embodiment, a table of operable pages may be stored in the designated block or blocks of the flash memory. For example, thorough testing of an entire flash memory device by a memory controller may occur when an indication is incomplete, unreadable, missing, or damaged. This type of testing may occur when the memory controller and/or flash memory devices are powered on for the first time. Additional tests, for example by an error correction code (ECC) module may be performed during operation of a flash memory device to detect pages that fail during use. Error detection methods used during flash memory operation may include, but are not limited to, generating checksums, comparing checksums, performing redundancy checks, generating parity values, performing parity checks, and executing other error detection algorithms. If a failure is detected in a page, the ECC module may alert the flash controller that a failure occurred or that an operation in progress was unsuccessful. The flash controller may then repeat the operation in a new page or otherwise correct the error. If a page has recoverable repeatable errors then that page is discarded. The master controller than takes appropriate action to exclude these pages by their designation in the table. From this point on the defective page is not used.

When one or more indications are updated, internal operations and data transfers may be completed to hide failures and reconfigurations from systems accessing the flash memory devices and ultimately from a human user of the flash memory devices. Consequently, a failure will not disturb the overall experience of a user and will not require compensation by outside systems. According to one embodiment, this may be accomplished with spare blocks, pages, and/or sectors that may be reserved during an initialization, testing, or other phase. As failures occur, data and addresses for failing blocks, pages, and/or sectors may be replaced by spare blocks, pages, and/or sectors. One or more indications may then be updated to reflect the new logical memory addresses and physical memory addresses for the data.

In summary, page based failure management in a flash memory controller allows a memory controller to access a "good page" table or other indicator of the functionality of each of the pages within flash memory blocks. The memory controller can then execute read, write and erase commands utilizing the operable pages in each block, even if the block contains one or more inoperable pages. The use of page mode allows for a significant extension of the life of the flash memory. Further, the use of page mode allows for more efficient use of flash memory that has lower lifetime ratings and/or a higher number of errors. Rather than discard these flash memory chips with errors, these chips can be effectively used and have an extended lifetime in a device that implements page mode failure management as described above

The memory controller accepts data from the high speed internal bus using DMA protocols, accumulates the data in its internal buffers and writes the data to the NAND flash die. Each flash memory module is configured to provide data transfer speeds of approximately 40 megabytes per second to and from the flash die. These parallel flash memory modules may have a number of configurations, including those described in U.S. Pat. App. No. 61/774,175; entitled "High Speed USB Controllers," to Charles Peddle, which is hereby incorporated by reference in its entirety. For

example, there may be parallel eight flash memory modules. In one implementation each of the flash drives includes four flash dies. Each flash die includes 8 Gigabytes of storage, resulting in a total flash storage of 256 Gigabytes. These drives are configured to operate in parallel, providing 5 approximate transfer rates of 320 Megabytes per second for data writing. Reading data from flash memory is significantly faster than writing data to the flash memory. Consequently, the flash memory modules may exhibit correspondingly higher data transfer rates during reading operations. 10 Moving Data Between the CPU Memory, DRAM Logical Flash, and Flash Memory

FIG. 4 is a diagram that shows an overview of various methods used to transfer data between the CPU memory, DRAM logical flash, and flash memory. Each of the methods 15 for transferring data is described in more detail in the figures and description below.

The system shown in FIG. 4 includes a CPU that is operably connected to a CPU memory. As shown in FIG. 3, the CPU and CPU memory are connected to the DRAM 20 logical flash in the solid state drive by the system bus (SATA bus). The DRAM logical flash is connected to the flash memory by a high speed internal bus. As discussed above, the movement of data between the DRAM logical flash and the flash memory is independently managed by the master 25 controller. The master controller may act in response to commands received from the CPU, but CPU has no direct control over transfers to the flash memory and is unaware that these transfers occur.

The system can implement a variety of data transfers 30 between memories to accomplish specific objectives. In general, the computing device sends commands about data collections called files. The commands are quite simple: read this file, write the file, or update an existing file. The command comes to the SSD as SATA commands which are 35 interpreted by the master controller. The data from the external bus is streamed into the logical flash at full speed and the logical flash controller is directed to store or replace previous versions of the associated data file. The external bus may be a SATA bus, USB bus, or any other appropriate 40 protocol or technology. When the computing device wants to read back a file or part of a file, the read command is initially given to the logical controller which is directed to retrieve the desired data from data stored in its memory. If the data is not in the DRAM logical flash, it is stored there under 45 direction of the master controller from the flash devices and then transferred at high speed to the computing device. This data is maintained in the DRAM logical flash because it is likely to be updated and reloaded.

One approach described in PCT/US14/20406, entitled 50 "High Speed Flash Controllers," which is incorporated herein in its entirety by reference, is to fix write errors in the individual flash controllers by rewriting data from the DRAM to the pages which are found to have a write error. The block value is then downgraded to eliminate the page 55 found to have the error from further use. After a write operation is completed, under the principles disclosed herein, the master controller causes the written data to be compared with the corresponding data in the DRAM. Any data that does not match is rewritten in the SSD using the 60 same technique described above for write errors generally.

FIG. 4 shows illustrative examples of five different data transfer techniques. A first technique is data transfer using logical records which is described in greater detail in FIGS. 5A, 5B, 6A, and 6B. The processor deals with logical 65 records while the controllers deal with physical records. A translation table is used to convert/index the relationship

14

between logical records and physical records. The translation table used for the SSD differs from the translation tables used in hard disk storage systems. This data transfer technique uses logical records to index and store data from the CPU memory to the working area of the DRAM logical flash as directed by the CPU and to subsequently store data files that are not being used to the working area of the flash memory under direction of the master controller. The master controller also directs retrieval of the data out of the working area in the flash memory into the working area of the DRAM logical flash for direct retrieval by the CPU memory.

A second data transfer technique is snapshot flow that allows for snapshots of the system state to be saved periodically so that the system can be recovered to a previous state. This technique is described in greater detail in FIG. 7. In this implementation, the data is transferred to a specified snapshot area within the DRAM logical flash without the use of logical records. Other techniques, such as tables, can be used to index and recover the snapshot data. In one example, the snapshots are indexed by time. The most recent snapshots are most valuable in recovering the state of the computing device. The older snapshots are overwritten by new snapshots during the use of the system. This stores the most recent snapshots for use in future recovery operations. The snapshots are stored DRAM logical flash and are not transferred into the flash memory until power down. On power down, only selected numbers of the snapshots are stored to the flash memory as part of the dump process. This can significantly increase the lifetime of the flash memory by reducing the number of writes made to the flash memory. In contrast, Apple notebooks store the snapshots directly to flash memory. This snapshot operation occurs frequently during use of the notebooks and results in significant flash wear.

A third data transfer/storage technique is the FastLoad process described in FIG. 8. The FastLoad process includes a protected program area in the flash memory that stores program files. In this example, the protected program area in the flash memory has two divisions, one for stored programs and one for active programs. The FastLoad process is implemented by additional circuitry and logic that are not part of a standard controller using DRAM flash. When the user obtains permission to access the stored programs, the FastLoad process can be used to move the program files to a protected program area in the DRAM logical flash. From there, the CPU can request the program files to be transferred to the CPU memory for execution.

A fourth data transfer/storage technique is a dump/recovery process described in more detail in FIG. 9. The dump/recovery process occurs on power down or power loss. The dump/recovery process moves data out of the DRAM logical flash into a specified dump area in the flash memory. To recover, power is restored to the computing device and the data in the dump area is transferred back into DRAM logical flash and then to the CPU memory.

A fifth data transfer technique is a mishandled file recovery technique described in FIG. 10. A "mishandled" refers to any instance where an unintended and undesired change is made to a file. For example, all or a portion of a file may be deleted, or a desired file may be overwritten by another file. The mishandled file recovery technique provides for recovery of a file that the CPU has instructed to be deleted from the DRAM logical flash to be recovered from the DRAM logical flash. The DRAM logical flash has a latency period during which the mishandled files can remain stored in the DRAM logical flash. A limited history file is used to index

and recover these mishandled files that still reside on the DRAM logical flash. Each of these techniques is described below

Although the DRAM logical flash is illustrated as an integral physical part of the SSD, in some implementations, 5 the DRAM logical flash may be constructed in the CPU volatile memory, with the CPU providing the control of reading, writing, and flash operations of the DRAM logical flash. However, in conventional CPU/CPU memory systems, there is no mechanism to maintain the power while 10 dumping the data to the volatile CPU memory when the power goes down. To successfully implement the principles discussed herein, the computing device could have an independent power source to allow the data stored in the CPU memory to be dumped from the DRAM logical flash to the 15 flash in the solid state drive.

Additionally, the DRAM logical flash may be used or configured to perform only part of the functions described above. For example, the DRAM logical flash may be configured to provide FastLoad operations or Snapshot opera- 20 tions without being used for logical record type data transfers. This may significantly simplify the operation of the DRAM logical flash. In other implementations, the DRAM logical flash may be segmented into operationally specific parts. The volatile memory associated with the microcon- 25 troller may be mapped into a snapshot/fastload segment (areas) and logical record segments (areas). The snapshot/ fastload segment may store data that is transferred to the flash using special protocols and may or may not be indexed by logical records. In some circumstances the amount of 30 DRAM logical flash may be increased to accommodate this mapping into separate segments/areas.

For example, the non-logical record area may store snapshot data or fastload data. The data in the non-logical record area may or may not be loaded into the flash. For example, 35 if the non-logical record area of the memory contains 4 snapshots that can be used to recover the state of the computing device, only one or two of the most recent snapshots may actually be saved to the flash on power down. The other older snapshots are simply discarded.

In another example, fastload programs may be loaded into the non-logical record area of the volatile memory. These fastload programs are executables that are typically modified during normal operation and are not written back to the flash memory. There is an alternative logical path for updating the 45 programs. This alternative logical path allows software programmers to update the software. Restrictions and protocols may restrict anyone other than the software distributors from accessing the authorized software programmers from accessing this area. This is because there are specific 50 commands for these areas that are not disclosed to any unauthorized individuals or entities.

In order to protect copying of software, the operating system may not allow the copying of code loaded to the fastload to user ports or any other port in the system. 55 Fastload is, in general, a read only function for the users. This prevents modification and distribution of the programs by the users. As discussed above, there may be separate commands in the protocol that are available only to the software publishers (or other authorized users) so that only 60 they can update the software.

In other examples, there may be multiple separate memory controllers. In one implementation there may be one controller for the standard volatile memory included in the memory device and one for the DRAM logical flash. 65 Further, the standard volatile memory may be protected and not directly addressable or accessible to the user and or

16

computing device. In some instances, the standard volatile may have special restrictions or usage. In some embodiments, the memory may appear to be an extension of the system volatile memory.

Writing Files to the Solid State Drive

During ordinary operation the CPU uses the same protocols to write files to the SSD that it would use to write data to a typical hard drive. For example, the CPU may use the technique of writing and reading to the SSD using logical records. The internal operations of the SSD drive are independent from the CPU operations and are hidden from the CPU. As discussed above, the SSD drive accepts the data from CPU, but internally manages and stores the data in a unique manner that overcomes speed and lifetime limitations of the NAND flash memory. However, the SSD drive controls the interface between the SSD drive and the CPU so that it fully appears to the CPU that it is writing to hard drive or ordinary flash drive. Consequently, the SSD is a plug and play memory storage device that can be used in any of a variety of computing devices and transparently provides superior data transfer rates, long lifetime, and low power consumption.

FIG. 5A is a diagram that shows illustrative data flow through the SSD architecture that allows for extremely fast data transfer rates. Data is initially transferred by CPU operations over the system bus. For example, the system bus may be a SATA bus. The data is transferred off the system bus using a DMA process to the DRAM logical flash. As discussed above, the DRAM logical flash stores the data for later retrieval by the CPU. The CPU is only aware of the DRAM logical flash, which appears to be extremely fast non-volatile solid state memory with a memory capacity of the flash memory.

If the master controller determines that it is appropriate, the master controller decides to write data out of the DRAM logical flash to the flash memory. There may be any number of flash memory modules within the SSD. For example, the SSD architecture may include eight flash memory modules. For purposes of illustration, FIG. 5A shows only four of 40 those devices. As discussed above with reference to FIG. 3, each of the flash memory devices includes a memory controller with buffers and a number of flash memory die. For example, each flash memory controller may control distribution to four, eight, or sixteen separate die. The distribution of data among a number of flash memory controllers provides a number of benefits including simultaneous writing to multiple flash die. This compensates for the relative slow write times that are inherent in the current implementation of flash memory. The independence of the master controller and various flash memory controllers allows for parallel data transfer with minimal latency. To enable parallel writes and parallel reading operations, a file is striped across the various flash memory die. In FIG. 5A this is illustrated as numbered boxes in each of the flash memory die. When a file is written the master controller sequentially address the individual flash memory controllers, which in turn sequentially address the flash die they control. This results in the file being distributed across the die and various portions of the file being written in simultaneously to different flash die. When the file is retrieved from the flash die, it can be read from the die in parallel. This is shown in FIG. 6A.

An illustrative method for writing files to the SSD is shown in FIG. 5B. In a first step, the CPU sends a write command and places data to be written to the SSD on SATA bus (step 505). The write command is transferred to the master controller, which instructs the DRAM controller to

accept the data and transfer it to the DRAM memory (step 510). The DRAM controller may be configured to discriminate between commands and other data and send the commands to the master controller over a separate bus. This example, the DRAM controller sends a write commend to 5 the master controller. When the master controller interprets the write command, it alerts the DRAM controller that new data is coming. The DRAM controller looks for the logical records in the command and searches for the logical records in its tables to determine if the data is already contained in 10 the DRAM logical flash. For example, the current logical record maybe part of another bigger file. The DRAM controller is able to determine that the data is already in the DRAM logical flash by searching for the beginning and end logical record for each file. If the current logical record is 15 between the beginning and end logical record for each file, the data is currently stored in the DRAM logical flash and will be overwritten. To allow for mishandled file recovery as described below, the logical record data is written in a new space in the DRAM logical flash with a notation of the 20 address of the replaced file. However, if the logical record is not in DRAM logical flash and represents new data, a new record is created for the new logical record and the data is collected in the DRAM logical flash.

When the writing is complete with a FAT-based system, a 25 File allocation Table (FAT) is updated and sent by the CPU over the SATA interface. In some operating systems, the storage of each FAT table entry can involve multiple, redundant write cycles. If the FAT table is requested from the SSD, the request is serviced from the DRAM logical flash. The 30 FAT tables are stored in the DRAM logical flash and only saved to the flash memory on power down. This can save thousands of erase/write cycles in the flash memory.

In contrast, NTFS is a journaling file system. Thus, NTFS uses a log file to record metadata changes to the volume. In 35 this way, NTFS ensures that its internal complex data structures (notably the volume allocation bitmap), or data moves performed by the defragmentation API, the modifications to MFT records (such as moves of some variable-length attributes stored in MFT records and attribute lists), 40 and indices (for directories and security descriptors) will remain consistent in case of system crashes, and allow easy rollback of uncommitted changes to these critical data structures when the volume is remounted. As noted above, this approach results in even more frequent writing to the 45 SSD that does the FAT system

The logical flash controller sets up the SATA DMA and manages the transfer of the data into the DRAM logical flash (step 515). As discussed above, the DRAM memory used in the DRAM logical flash is extremely fast random access 50 memory. The combination of DMA transfers, a dedicated DRAM controller, and the extremely fast DRAM memory means that data stored in the DRAM logical flash is easily and rapidly accessible to the CPU at speeds that are typically limited by the SATA bus. The DRAM logical flash is used 55 to store data that is frequently accessed. This insulates the flash memory devices in the SSD from excessive write cycles. The logical flash controller manages the data in the DRAM as flash files, including using flash techniques to consolidate and update the data (step 520). This allows the 60 DRAM logical flash to interface with the SATA bus in the same way as standard flash memory, but at much higher speeds.

There is no temporal correlation between SATA data and the flash data. The flash memory and data stored on the flash 65 memory is not directly accessible to the CPU, but is controlled by master controller. The CPU interfaces only with

18

the DRAM logical flash, with command data being transferred from the DRAM logical flash to the master controller. The logical flash controller periodically evaluates the usage of the data and determines if the data should be written from the DRAM logical flash to the NAND flash memory (step 525). For example, a file that is in use by the CPU may be saved regularly to the SSD drive during the time that the user is working with the file. After the user is finished with the file, the file can be dormant for days or months before it is again accessed. The data stored in the DRAM logical flash is written at specified save points to the NAND flash memory. For example, the data stored in the DRAM logical flash may be transferred to the NAND flash memory when the file is closed or when the computer is powered down. Other save points may occur when the capacity of the DRAM logical flash is mostly consumed. In this case, a file that is less frequently saved can be transferred to the flash memory.

The transfer of data from the DRAM logical flash to the NAND flash memory under control of the master controller will now be described. When the master controller makes the decision to write the data from the DRAM logical flash to the flash memory devices, it sends a command to the logical flash controller that identifies the data that is to be transferred and alerts the bus controller of the data transfer (step 530). The master controller places command data onto the internal bus that alerts/enables the flash controllers so that they can receive/retrieve the desired data. The logical flash controller sets the appropriate register values to configure the internal bus DMA for the transfer and the data identified by the master controller is placed on the high speed internal bus by the bus DMA (step 535). The master controller (or alternatively the optional bus controller) then begins transfer of the data with specific data segments addressed to individual flash controllers (step 540). A variety of techniques can be used to manage the transfer of data over the high speed internal bus. In one implementation, data that is loaded onto the internal bus includes a marker indicating the beginning of the data sequence, a marker indicating the end of the data sequence, and a structure than identifies the component the data is addressed to. Each flash controller watches for its identifier in the data stream and diverts the appropriate data segments to its internal storage. In other implementations, there may be a separate command/enable lines that are connected to each of the memory controllers. When data is intended for a specific flash memory module, the enable line connected to this memory controller is asserted while the enable lines for the other memory controllers are not asserted. This configuration is shown in FIG.